# 80A, 75V N-Channel MOSFET

# **General Description**

GGVD75N08T is an N-channel enhancement mode MOS field effect transistor which is produced using Silan new structure VDMOS technology. The improved planar stripe cell and the improved guard ring terminal have been especially tailored to minimize on-state resistance, provide superior switching performance, and withstand high energy pulse in the avalanche and commutation mode. Optimize the parasitic parameters of the device and enhance the anti-jamming capability of the gate, which make it easy to use in parallel. These devices are widely used in AC-DC power suppliers, DC-DC converters and H-bridge PWM motor drivers.

### **Features**

- 80A, 75V, RDS(on) (typ.) =9mΩ@VGS=10V

- Low gate charge

- Low Crss

- Fast switching

- Improved dv/dt capability

## **Ordering Information**

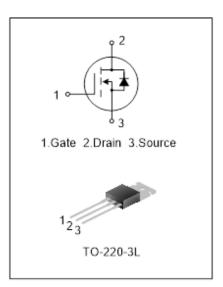

| Part No.   | Package   | Marking    | Material | Packing |

|------------|-----------|------------|----------|---------|

| GGVD75N08T | TO-220-3L | GGVD75N08T | Pb free  | Tube    |

### Absolute Maximum Ratings (TC=25 C unless otherwise noted)

| Characteristics                          |                      | Symbol           | Rating              | Unit |

|------------------------------------------|----------------------|------------------|---------------------|------|

| Drain-Source Voltage                     |                      | V <sub>DS</sub>  | 75                  | V    |

| Gate-Source Voltage                      |                      | V <sub>GS</sub>  | V <sub>GS</sub> ±20 |      |

| Drain Current                            | T <sub>C</sub> =25℃  |                  | 80                  |      |

|                                          | T <sub>C</sub> =100℃ | ID               | 70                  | A    |

| Drain Current Pulsed                     |                      | I <sub>DM</sub>  | 300.0               | А    |

| Power Dissipation( $T_{C}=25^{\circ}C$ ) |                      |                  | 300                 | W    |

| -Derate above 25°C                       |                      | PD               | 2.40                | W/°C |

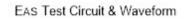

| Single Pulsed Avalanche Energy (Note 1)  |                      | E <sub>AS</sub>  | 844                 | mJ   |

| Operation Junction Temperature Range     |                      | TJ               | -55~+150            | °C   |

| Storage Temperature Range                |                      | T <sub>stg</sub> | -55~+150            | °C   |

## **THERMAL CHARACTERISTICS**

| Characteristics                         | Symbol             | Rating | Unit |

|-----------------------------------------|--------------------|--------|------|

| Thermal Resistance, Junction-to-Case    | $R_{	ext{e}_{JC}}$ | 0.42   | °C/W |

| Thermal Resistance, Junction-to-Ambient | R <sub>eja</sub>   | 62.50  | °C/W |

### **ELECTRICAL CHARACTERISTICS** (T<sub>c</sub>=25°C unless otherwise noted)

| Characteristics                          | Symbol              | Test conditions                                                                                         | Min. | Тур. | Max. | Unit |

|------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|------|------|------|------|

| Drain –Source Breakdown Voltage          | B <sub>VDSS</sub>   | V <sub>GS</sub> =0V, I <sub>D</sub> =250µA                                                              | 75   |      |      | V    |

| Drain-Source Leakage Current             | I <sub>DSS</sub>    | $V_{DS}=75V, V_{GS}=0V$                                                                                 |      |      | 1.0  | μA   |

| Gate-Source Leakage Current              | I <sub>GSS</sub>    | $V_{GS}=\pm 20V, V_{DS}=0V$                                                                             |      |      | ±100 | nA   |

| Gate Threshold Voltage                   | V <sub>GS(th)</sub> | $V_{GS} = V_{DS}, I_D = 250 \mu A$                                                                      | 2    |      | 4.0  | V    |

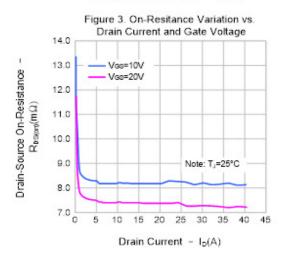

| Static Drain- Source On State Resistance | R <sub>DS(on)</sub> | V <sub>GS</sub> =10V, I <sub>D</sub> =40 A                                                              |      | 9    | 12   | mΩ   |

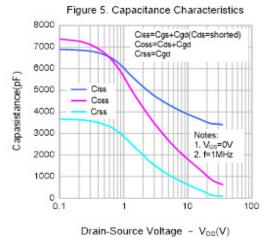

| Input Capacitance                        | C <sub>iss</sub>    | V <sub>DS</sub> =25V,V <sub>GS</sub> =0V, f=1.0MHZ                                                      |      | 3486 |      |      |

| Output Capacitance                       | C <sub>oss</sub>    |                                                                                                         |      | 790  |      | pF   |

| Reverse Transfer Capacitance             | C <sub>rss</sub>    |                                                                                                         |      | 143  |      |      |

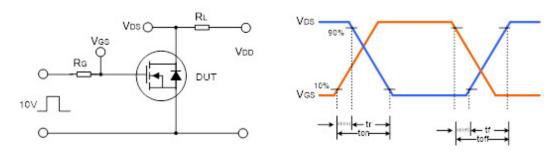

| Turn-on Delay Time                       | t <sub>d(on)</sub>  | V <sub>DD</sub> =40V, V <sub>GS</sub> =10V,<br>R <sub>G</sub> =25Ω, I <sub>D</sub> =37.5A<br>(Note 2,3) |      | 55   |      |      |

| Turn-on Rise Time                        | tr                  |                                                                                                         |      | 229  |      |      |

| Turn-off Delay Time                      | t <sub>d(off)</sub> |                                                                                                         |      | 260  |      | ns   |

| Turn-off Fall Time                       | t <sub>f</sub>      |                                                                                                         |      | 124  |      |      |

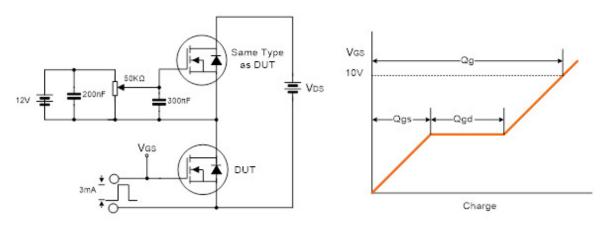

| Total Gate Charge                        | Qg                  | V <sub>DS</sub> =60V, I <sub>D</sub> =75A,                                                              |      | 93   |      |      |

| Gate-Source Charge                       | Q <sub>gs</sub>     | V <sub>GS</sub> =10V                                                                                    |      | 20   |      | nC   |

| Gate-Drain Charge                        | Q <sub>gd</sub>     | (Note 2,3)                                                                                              |      | 44   |      |      |

## **SOURCE-DRAIN DIODE RATINGS AND CHARACTERISTICS**

| Characteristics           | Symbol          | Test conditions                          | Min. | Тур. | Max.  | Unit |

|---------------------------|-----------------|------------------------------------------|------|------|-------|------|

| Continuous Source Current | ls              | Integral Reverse P-N                     |      |      | 80    |      |

| Pulsed Source Current     | I <sub>SM</sub> | Junction Diode in the<br>MOSFET          |      |      | 300.0 | A    |

| Diode Forward Voltage     | $V_{SD}$        | I <sub>S</sub> =80A,V <sub>GS</sub> =0V  | -    |      | 1.5   | V    |

| Reverse Recovery Time     | T <sub>rr</sub> | I <sub>S</sub> =80A,V <sub>GS</sub> =0V, |      | 91   |       | ns   |

| Reverse Recovery Charge   | Q <sub>rr</sub> | dI <sub>F</sub> /dt=100A/µS (Note 2)     |      | 0.33 |       | μC   |

#### Notes:

- 1. L=0.24mH,  $I_{AS}$ =85A,  $V_{DD}$ =35V,  $R_G$ =25 $\Omega$ , starting  $T_J$ =25°C;

- 2. Pulse Test: Pulse width ≤300µs,Duty cycle≤2%;

- 3. Essentially independent of operating temperature.

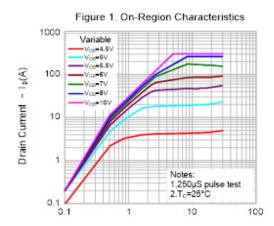

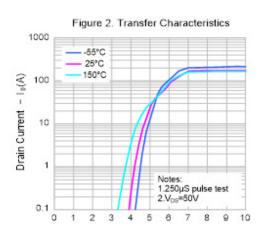

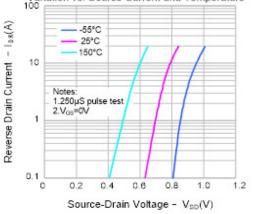

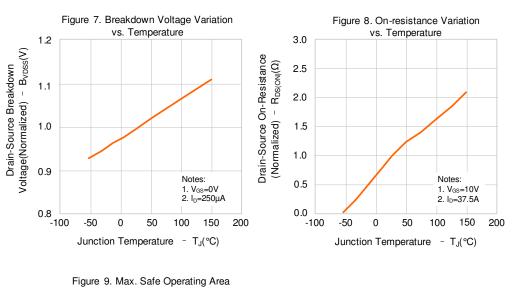

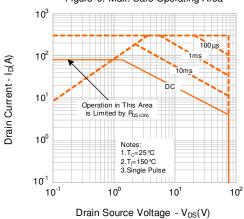

## **TYPICAL CHARACTERISTICS**

Drain-Source Voltage - V<sub>DS</sub>(V)

Gate-Source Voltage - V<sub>GS</sub>(V)

Figure 4. Body Diode Forward Voltage Variation vs. Source Current and Temperature

Figure 6. Gate Charge Characteristics 12 V<sub>DS</sub>=60V Source Voltage - V<sub>GS</sub>(V) V<sub>DS</sub>=40V 10 V<sub>DS</sub>=20V 8 6 4 Gate-2 Note: Ip=75A 0 0 20 40 60 80 100 120 Total Gate Charge - Qg(nC)

Golden Gate Integrated Circuits, Inc. www.goldengate-ic.com

# **Typical Characteristics (Continued)**

## **TYPICAL TEST CIRCUIT**

Gate Charge Test Circuit & Waveform

### Switching Test Circuit & Waveform

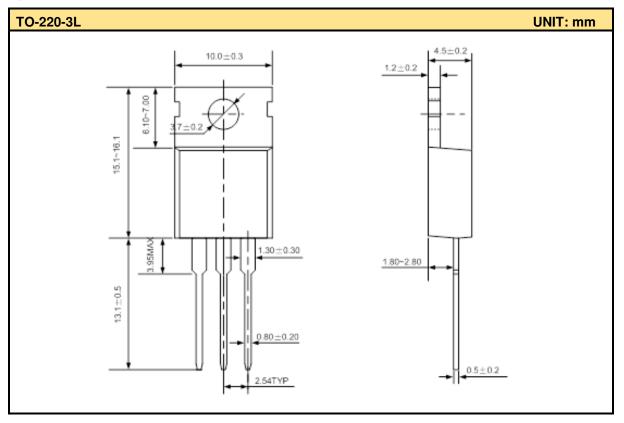

# **Package Outline**

### **Disclaimer:**

The information furnished in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Golden Gate Integrated Circuits (GGIC) for its use. GGIC reserves the right to change circuitry and specifications at any time without notification to the customer.

- Golden Gate Integrated Circuits reserves the right to make changes to the information herein for the improvement of the design and performance without further notice! Customers should obtain the latest relevant information before placing orders and should verify that such information is complete and current.

- All semiconductor products malfunction or fail with some probability under special conditions. When using Golden Gate Integrated Circuits

products in system design or complete machine manufacturing, it is the responsibility of the buyer to comply with the safety standards strictly and

take essential measures to avoid situations in which a malfunction or failure of such Golden Gate Integrated Circuits products could cause loss of

body injury or damage to property.

- Golden Gate Integrated Circuits (GGIC) Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of GGIC Products for use in life support appliances, devices, or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify GGIC for any damages resulting from such use or sale.